- Integrated, Single-Chip Solution for Battery Charge Control and Power Supply Management

- Linear Charger for Single-Cell Li-Ion or Li-Polymer Packs

- Integrated Control Over Precharge, Constant-Current and Constant-Voltage Charging Phases

- Programmable Charging Current

- Programmable Charge Termination by Minimum Current and Time

- Battery Temperature Sensing

- Pack Wake Up and Damaged Cell Detect Functions

- Safety Charge Timers During Precharge and Constant-Current Charging

- Six Programmable Low-Dropout Linear Voltage Regulators

- System Over- and Under-Voltage Shut Down

- Power On/Power Off and Reset Control Logic

- Three Individually Selectable LED Backlight Drivers

- Vibrator and Ringer Drivers

- Internal 8-Bit Analog-to-Digital Converter (ADC) with Auxiliary Inputs

- I<sup>2</sup>C Control Interface

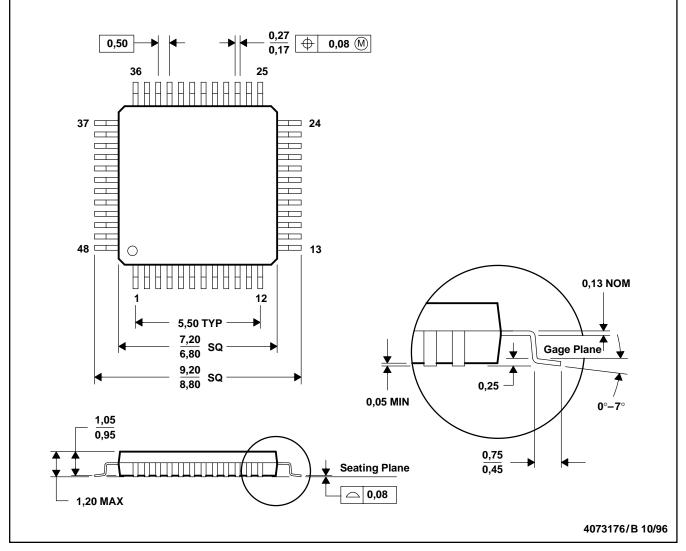

- 48-Terminal Plastic TQFP(PFB)

# description

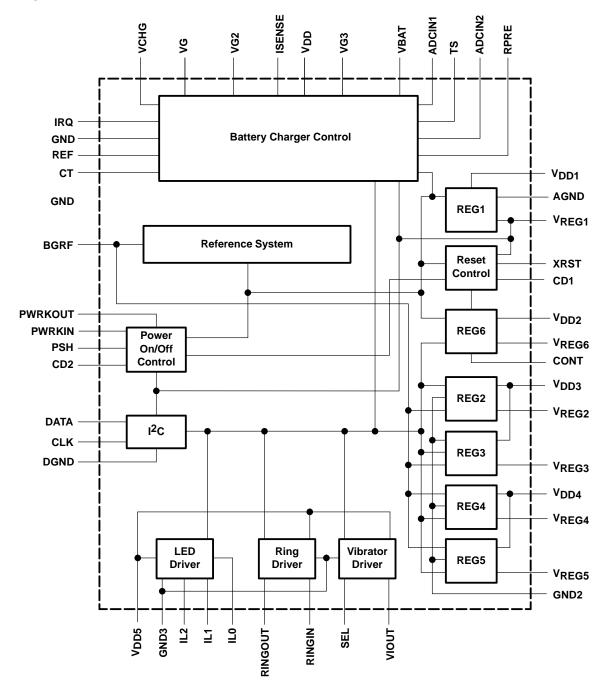

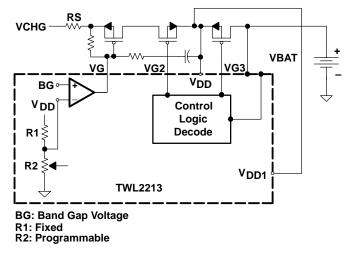

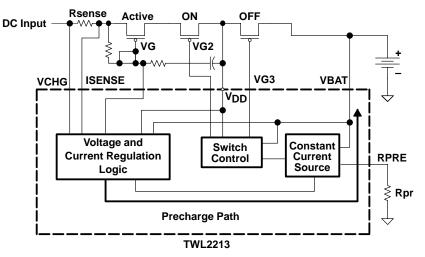

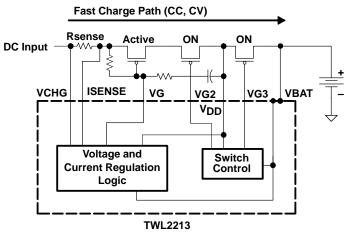

The TWL2213 is a single-chip battery and power management solution for wireless handsets, pagers, personal data assistants (PDAs), and other battery-powered devices. For battery charging, the device incorporates a linear charger for single-cell Li-lon and lithium polymer battery packs. Prior to charging, the TWL2213 initiates battery pack wake up and damaged cell detect functions. For deeply discharged batteries, the device performs precharge conditioning by trickle-charge to user-defined current settings. Once acceptable pack voltage is detected, TWL2213 applies a constant-current fast charge at a current level that is determined by a combination of an external sense resistor and user-programmable sense voltage. When the battery reaches the selected charge regulation voltage, TWL2213 maintains regulation until charging is terminated by a minimum current or a timer. During the entire charge cycle, TWL2213 monitors temperature by external thermistor and suspends charging if temperature exceeds a programmed range. Three programmable safety timers limit the precharge, constant-current, and total charge times.

For power management, the TWL2213 includes six low-dropout linear voltage regulators. One regulator is driven from the device's power on/off logic and incorporates a microcontroller reset function. Five low noise regulators include individually programmable output voltage and enable-disable. The TWL2213 can be powered from a battery or AC adapter. When an adapter is present, it supplies power to the device, allowing the system to function without battery.

TWL2213 also includes individually selectable drivers for three separate backlight LEDs, a ringer, and a vibrator motor. An internal 8-bit analog-to-digital converter (ADC) is accessible from external pins. The system microcontroller accesses all TWL2213 programming and status via the I<sup>2</sup>C serial interface.

The TWL2213 device is packaged in the Texas Instruments 48-terminal plastic thin quad flatpack (TQFP) package (PFB).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2001, Texas Instruments Incorporated

|               | A                                                                                                                                                                                    | VAILABLE OPTIONS                                                       |                                                                                                                                                                                                                                              |                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| т.            | DEVICE NAME                                                                                                                                                                          | DACKACE                                                                | OUTPUT                                                                                                                                                                                                                                       | VOLTAGE            |

| TA            |                                                                                                                                                                                      | PACKAGE                                                                | <b>REGULATOR 1</b>                                                                                                                                                                                                                           | <b>REGULATOR 6</b> |

| -40°C to 85°C | TWL2213CAPFBR                                                                                                                                                                        | TQFP                                                                   | 2.8 V                                                                                                                                                                                                                                        | 3 V                |

| F             | RKOUT [ 37<br>WRKIN [ 38<br>PSH [ 39<br>DATA [ 40<br>CLK [ 41<br>CD2 [ 42<br>DGND [ 43<br>VIOUT [ 44<br>V <sub>DD5</sub> [ 45<br>NGOUT [ 46<br>RINGIN [ 47<br>GND3 [ 48<br>0 1 2 3 4 | PFB PACKAGE<br>(TOP VIEW)<br>BSN 2 C C C C C C C C C C C C C C C C C C | 24 ] TS<br>23 ] ADCIN1<br>22 ] ADCIN2<br>21 ] CONT<br>20 ] V <sub>REG5</sub><br>19 ] V <sub>DD4</sub><br>18 ] V <sub>REG4</sub><br>17 ] BGRF<br>16 ] GND2<br>15 ] V <sub>REG3</sub><br>14 ] V <sub>DD3</sub><br>13 ] V <sub>REG2</sub><br>12 |                    |

### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> = 25°C | OPERATING FACTOR | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE 25°C       | POWER RATING          | POWER RATING          |

| PFB     | 1962 mW               | 15.7 mW/C        | 1256 mW               | 1020 mW               |

SLVS280 - MARCH 2001

# block diagram

# **Terminal Functions**

| TERMINAL         |         |     |                                                                                                                |

|------------------|---------|-----|----------------------------------------------------------------------------------------------------------------|

| NAME             | PFB NO. | 1/0 | DESCRIPTION                                                                                                    |

| ADCIN1           | 23      | I   | ADC input                                                                                                      |

| ADCIN2           | 22      | I   | ADC input                                                                                                      |

| AGND             | 8       | I/O | Regulator 1 ground                                                                                             |

| BGRF             | 17      | I/O | Band gap output bypass capacitance                                                                             |

| CD1              | 9       | I/O | XRST output delay adjustment capacitance                                                                       |

| CD2              | 42      | I/O | Regulator 1 off delay adjustment capacitance                                                                   |

| CLK              | 41      | I   | I <sup>2</sup> C bus serial clock input                                                                        |

| CONT             | 21      | I   | Regulator 6 is always on after power up except when CONT = H; regulator 6 is enabled through $I^2C$ interface. |

| СТ               | 35      | I/O | External oscillator timing cap                                                                                 |

| DATA             | 40      | I/O | I <sup>2</sup> C bus serial address/data input output; this is a bidirectional terminal                        |

| DGND             | 43      | I/O | Digital ground                                                                                                 |

| GND              | 12, 34  | I/O | Ground                                                                                                         |

| GND2             | 16      | I/O | Ground for VREG2, VREG3, VREG4, and VREG5                                                                      |

| GND3             | 48      | I/O | Vibrator, LED, ringer ground                                                                                   |

| IL0              | 1       | 0   | 160-mA LED driver output                                                                                       |

| IL1              | 2       | 0   | 20-mA LED driver output                                                                                        |

| IL2              | 3       | 0   | 10-mA LED driver output                                                                                        |

| IRQ              | 36      | 0   | Interrupt signal for external controller regarding to charger START/STOP action                                |

| ISENSE           | 31      | 1   | Current sense input for charger function                                                                       |

| PSH              | 39      | I   | Power hold signal from controller                                                                              |

| PWRKIN           | 38      | I   | Power-up start                                                                                                 |

| PWRKOUT          | 37      | 0   | Power-up signal for CPU                                                                                        |

| REF              | 25      | 0   | Voltage reference during charge cycle, 3 V, $I_{O}$ = 3 mA                                                     |

| RINGIN           | 47      | I/O | Input for ring driver                                                                                          |

| RINGOUT          | 46      | 0   | Ring driver output                                                                                             |

| RPRE             | 33      | I/O | Precharge current sense resistor                                                                               |

| SEL              | 4       | I   | Input for vibrator output voltage change                                                                       |

| TS               | 24      | I   | Battery temperature sense input voltage                                                                        |

| VBAT             | 26      | I/O | Battery voltage sense input or output for precharge, wakeup                                                    |

| VCHG             | 32      | I   | DC voltage input for charger                                                                                   |

| V <sub>DD</sub>  | 28      | I   | Device dc supply feedback for charger function                                                                 |

| V <sub>DD1</sub> | 5       | I   | Device dc supply input and regulator 1 input                                                                   |

| V <sub>DD2</sub> | 11      | I   | Input to regulator 6                                                                                           |

| V <sub>DD3</sub> | 14      | I   | Input for regulators 2 and 3                                                                                   |

| V <sub>DD4</sub> | 19      | I   | Input for regulators 4 and 5                                                                                   |

| V <sub>DD5</sub> | 45      | I   | Input for vibrator, PN diode connection of ringer                                                              |

| VG               | 30      | 0   | Gate control of an external P-FET for charger regulation                                                       |

| VG2              | 29      | 0   | Gate control of an external P-FET for battery blockage                                                         |

| VG3              | 27      | 0   | Gate control of an external P-FET for charging action                                                          |

| VIOUT            | 44      | I/O | Vibrator output                                                                                                |

SLVS280 - MARCH 2001

| Т                 | TERMINAL |       | DECODIDION         |

|-------------------|----------|-------|--------------------|

| NAME              | PFB NO.  | - I/O | DESCRIPTION        |

| V <sub>REG1</sub> | 6        | 0     | Regulator 1 output |

| V <sub>REG2</sub> | 13       | 0     | Regulator 2 output |

| V <sub>REG3</sub> | 15       | 0     | Regulator 3 output |

| V <sub>REG4</sub> | 18       | 0     | Regulator 4 output |

| V <sub>REG5</sub> | 20       | 0     | Regulator 5 output |

| V <sub>REG6</sub> | 10       | 0     | Regulator 6 output |

| XRST              | 7        | 0     | Reset output       |

# detailed description

# power on/off control

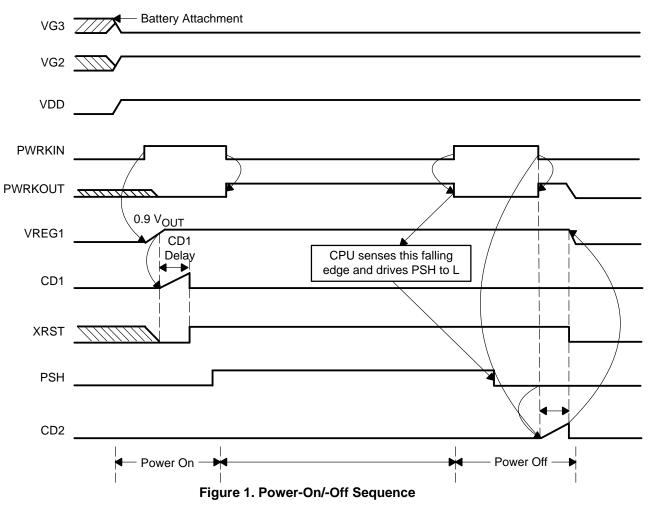

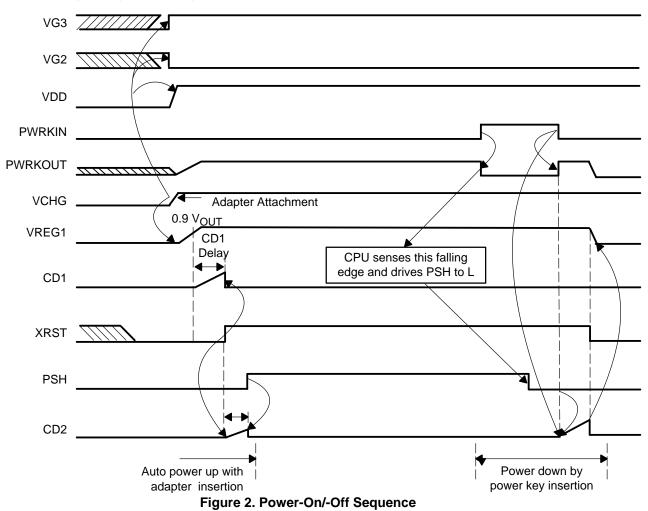

The power on/off control circuit controls the timing of the delayed power on reset. There are two different reset conditions: the manual power condition and the adapter power-on condition.

Under the manual-powered condition, if the power key is pressed, the PWRKIN signal goes high and V<sub>REG1</sub> (regulator 1 output) is enabled. After V<sub>REG1</sub> reaches 90% of its nominal output voltage, the TWL2213 starts the delayed reset process by charging the reset timing capacitor (CD1). When the voltage of CD1 reaches 1.2 V, the XRST signal is released by TWL2213 and is pulled high by an external pull-up resistor. This completes the reset process, and the external controller operates in normal condition. While the PWRKIN signal remains high, the power-on condition remains active. Before the PWRKIN signal goes low, the external controller must drive PSH high to retain power; otherwise, the TWL2213 starts the delay power-off process by charging the CD2 timing capacitor. After the voltage of CD2 reaches 1.2 V and no valid PSH signal is received, the device is powered off.

Under the adapter power-on condition, no battery is attached to the device. During the power-off state, after the adapter is attached, the output of  $V_{REG1}$  (regulator 1 output) is automatically enabled. After  $V_{REG1}$  reaches 90% of its nominal output voltage, the TWL2213 starts the delayed reset process by charging the reset timing capacitor (CD1). When the voltage of CD1 reaches 1.2 V, the XRST signal is released by TWL2213 and is pulled high by an external pull-up resistor. This completes the reset process, and the external controller operates in normal condition. The external controller must drive PSH high to retain power; otherwise, the TWL2213 starts the delay power-off process by charging the CD2 timing capacitor. After the voltage of CD2 reaches 1.2 V and no valid PSH signal is received, the device is powered off.

During the power-on state, the device generates an output signal (PWRKOUT) with the inverted polarity to PWRKIN. The external controller can use the PWRKOUT signal to detect power key action.

SLVS280 – MARCH 2001

# detailed description (continued)

detailed description (continued)

### reset controller

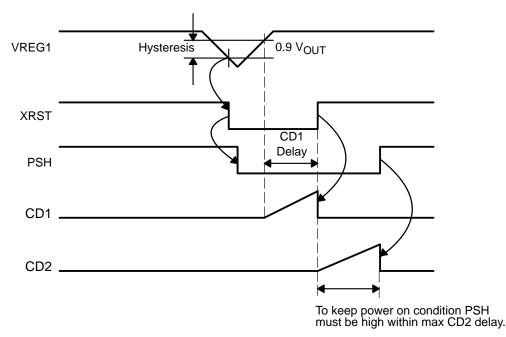

The reset controller performs two major functions; one is to control the timing of delayed power-on reset, and the other is to monitor the  $V_{REG1}$  level.

The delay reset process is started when  $V_{REG1}$  (regulator 1 output) reaches 90% of its nominal output voltage level. The delay time of the reset output (XRST) can be adjusted by external timing capacitance (CD1) (see Figure 1, and Figure 2).

During system active state when  $V_{REG1}$  drops below  $0.9V_{nominal}$  – hysteresis, XRST is driven low. If  $V_{REG1}$  reaches 90% of its nominal output voltage level again, the delayed reset process starts over.

# detailed description (continued)

Figure 3. V<sub>RFG1</sub> Monitoring of Reset Control

# regulator 1

This regulator is automatically enabled after the power-on process is complete. It stays enabled until the power-off condition occurs. Regulator 1 supplies power to the microprocessor. The nominal output voltage is 2.8 V, and the maximum output current is 150 mA. It requires an output capacitor in the range of 4.7  $\mu$ F-10  $\mu$ F with an equivalent serial resistance (ESR) less than  $6 \Omega$ .

### regulator 6

This regulator output voltage can be enabled by I<sup>2</sup>C/SPI by attaching the CONT terminal to  $V_{DD}$ . Attaching CONT to GND makes this regulator automatically enabled with power on. The output voltage is programmed by I<sup>2</sup>C/SPI. The maximum out current of 100 mA requires an output capacitor in range of 4.7  $\mu$ F-10  $\mu$ F, with ESR in the range of  $1\Omega - 6\Omega$ . The output voltage ranges from 2.5 V to 3 V.

# regulators 2, 3, 4, and 5

Regulators 2, 3, 4, and 5 are output voltages programmed and enabled by  $l^2C$ . The output voltage ranges from 2.3 V to 3 V in 100-mV steps. The maximum output current for regulators 2 and 3 is 80 mA, for regulator 4 it is 120 mA, and for regulator 5 it is 150 mA. The default output voltage for all regulators is 3 V. These regulators have very low output noise; this noise level is suitable for powering up the RF block, which requires an output capacitor in the range of 4.7  $\mu$ F-10  $\mu$ F with an ESR less than 6  $\Omega$ .

### vibrator driver

The TWL2213 device has incorporated a vibrator driver with selectable output voltage and current. This integrated vibrator driver has the same feature as the other load dropout (LDO) regulators. The vibrator is enabled by  $l^2$ C. The output voltage can be selected by tying the SEL terminal to V<sub>DD</sub> or GND. If the SEL terminal is tied to V<sub>DD</sub>, the output voltage is set to 3 V. If the SEL terminal is tied to GND, the output voltage is set to 1.3 V.

# detailed description (continued)

### LED driver

The TWL2213 device provides the capability of driving three LEDs. These drivers, enabled by I<sup>2</sup>C, can drive currents of 160 mA, 20 mA, and 10 mA individually with a maximum voltage drop of 0.8 V.

### ringer driver

The TWL2213 device provides the capability of driving a ringer. It is enabled by I<sup>2</sup>C and uses an N-channel FET with a maximum resistance of 3  $\Omega$ .

### l<sup>2</sup>C

This block provides I<sup>2</sup>C interface to the external devices.

### battery charger control

This block provides the necessary signals to control the external circuits that perform the charger function. The charging activities include battery pack wake up, precharge, fast charge, and battery temperature monitoring. This block also provides two ADC inputs for general measurement purpose. The input voltage level is from 0 to 2 volts. This block also includes an oscillator generator circuit, which generates the clocks for the device. The nominal frequency of the main clock is 500 kHz. It requires an external capacitor of 470 pF.

### reference system

This block provides voltage reference and bias current for the internal circuitry.

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| VCHG to GND (terminal 34)                            | –0.3 V to 12 V    |

|------------------------------------------------------|-------------------|

| All other terminals relative to GND                  | –0.3 V to 6.5 V   |

| Operating ambient temperature                        | −25°C to 85°C     |

| Operating junction temperature range, T <sub>J</sub> | . −25°C to 150°C  |

| Storage temperature range, T <sub>stg</sub>          | . – 55°C to 150°C |

| Soldering temperature (for 10 seconds)               | 260°C             |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

|                                           | MIN                 | MAX              | UNIT |

|-------------------------------------------|---------------------|------------------|------|

| VCHG                                      | 4.5                 | 6                | V    |

| V <sub>DD1</sub> - V <sub>DD5</sub>       | 3.3                 | 4.3              | V    |

| High-level logic input, PWRKIN, SEL, CONT | 0.7V <sub>DD1</sub> | V <sub>DD1</sub> | V    |

| Low-level logic input, PWRKIN, SEL, CONT  | GND                 | 0.3VDD1          | V    |

| High-level logic input, PSH               | 0.7VREG1            | VREG1            | V    |

| Low-level logic input, PSH                | GND                 | 0.3VREG1         | V    |

| Precharge current                         |                     | 100              | mA   |

SLVS280 - MARCH 2001

# electrical characteristics

# regulator 1 (C<sub>O</sub> = 4.7 $\mu$ F with ESR = 2 $\Omega$ )

|                 | PARAMETER        | TEST CONDITIONS                                                       | MIN  | TYP | MAX  | UNIT |

|-----------------|------------------|-----------------------------------------------------------------------|------|-----|------|------|

| VREG1           | Output voltage   | $I_{O} = I_{MAX}$                                                     | 2.68 | 2.8 | 2.91 | V    |

| lO              | Output current   | V <sub>DD1</sub> = 3.8 V                                              |      |     | 150  | mA   |

| l <sub>os</sub> | Short circuit    | V <sub>DD1</sub> = 3.8 V                                              |      |     | 550  | mA   |

|                 | Load regulation  | $I_{O} = 1 \text{ mA to } I_{MAX}, V_{DD1} = 3.8 \text{ V}$           |      |     | 80   | mV   |

|                 | Line regulation  | $V_{DD1} = 3.3 \text{ V to } 4.3 \text{ V}, I_{O} = I_{MAX}$          |      |     | 20   | mV   |

|                 | Dropout voltage  | IO = IMAX                                                             |      | 100 | 300  | mV   |

| kVIO            | Ripple rejection | f = 120 Hz, V <sub>DD1</sub> = 3.8 V                                  | 40   |     |      | dB   |

| I(Standby)      | Standby current  | $I_{O}$ = 1.5 mA (regulator 1 and internal bias circuitry are active) |      |     | 120  | μΑ   |

# regulator 6 (C<sub>O</sub> = 4.7 $\mu$ F with ESR = 2 $\Omega$ )

This 100 mA LDO can be enabled with serial interface I<sup>2</sup>C or by the CONT terminal. The output range is from 2.5 V to 3 V.

|                   | PARAMETER         | TEST CONDITIONS                                               | MIN    | TYP | MAX    | UNIT |

|-------------------|-------------------|---------------------------------------------------------------|--------|-----|--------|------|

|                   | Ontendentia       | CONT = Low                                                    | 2.88   | 3   | 3.12   | V    |

| V <sub>REG6</sub> | Output voltage    | CONT = High (see Note 1 and function register 4)              | 0.96Vp | Vp  | 1.04Vp | V    |

| IO                | Output current    |                                                               |        |     | 100    | mA   |

|                   | Short circuit     |                                                               |        |     | 330    | mA   |

|                   | Load regulation   | $I_O = 1 \text{ mA to } I_{MAX}, V_{DD2} = 3.8 \text{ V}$     |        |     | 70     | mV   |

| VS                | Line regulation   | $V_{DD2}$ = 3.3 V to 4.3 V, I <sub>O</sub> = I <sub>MAX</sub> |        |     | 20     | mV   |

|                   | Dropout voltage   | $I_{O} = I_{MAX}$                                             |        | 100 | 300    | mV   |

| KVIO              | Ripple rejection  | f = 120 Hz                                                    | 40     |     |        | dB   |

| ton               | Turnon time       | See Note 2                                                    |        |     | 150    | μs   |

| toff              | Turnoff time      | See Note 3                                                    |        | 2   | 5      | ms   |

| I(Quiescent)      | Quiescent current | I <sub>O</sub> = 1.5 mA                                       |        |     | 30     | μA   |

NOTES: 1. I<sup>2</sup>C-programmable.  $V_{(p)}$  is the programmed voltage. Refer to function registers 2 and 3 for programming information. 2. Output enable to output voltage =  $0.9 \times$  nominal value

3. Output disable to output voltage = 0.5 V

# electrical characteristics (continued)

# regulators 2, 3, 4, and 5 (C\_O = 4.7 $\mu\text{F}$ with ESR = 2 $\Omega\text{)}$

Regulators 2, 3, 4, and 5 provide programmable output. The output range, 2.3 V to 3 V, can be programmed in 100-mV steps.

|                  | PARAMETER             | TEST CONDITIONS                                                                 | MIN                | TYP | MAX                | UNIT          |

|------------------|-----------------------|---------------------------------------------------------------------------------|--------------------|-----|--------------------|---------------|

| VO               | Output voltage        | See Note 1                                                                      | 0.96V <sub>p</sub> | Vp  | 1.04V <sub>p</sub> | V             |

|                  |                       | Regulator 2                                                                     |                    |     | 80                 |               |

|                  |                       | Regulator 3                                                                     |                    |     | 80                 |               |

| 10               | Output current        | Regulator 4                                                                     |                    |     | 120                | mA            |

|                  |                       | Regulator 5                                                                     |                    |     | 150                |               |

|                  |                       | Regulator 2                                                                     |                    |     | 300                |               |

|                  |                       | Regulator 3                                                                     |                    |     | 300                |               |

|                  | Short-circuit current | Regulator 4                                                                     |                    |     | 400                | mA            |

|                  |                       | Regulator 5                                                                     |                    |     | 500                |               |

|                  |                       | Regulator 2, $I_0 = 1$ mA to $I_{MAX}$                                          |                    |     | 70                 |               |

|                  | Load regulation       | Regulator 4, $I_0 = 1$ mA to $I_{MAX}$                                          |                    |     | 50                 | mV            |

|                  |                       | Regulators 3 and 5, $I_0 = 1$ mA to $I_{MAX}$                                   |                    |     | 50                 |               |

|                  | Line regulation       | V <sub>I</sub> = 3.3 V to 4.3 V                                                 |                    |     | 20                 | mV            |

| V(dropout)       | Dropout voltage       | IO = IMAX                                                                       |                    |     | 300                | mV            |

| K <sub>VIO</sub> | Ripple rejection      | f = 10 kHz                                                                      | 40                 |     |                    | dB            |

| Ν                | Output noise          | $f = 10 \text{ Hz to } 100 \text{ kHz}, I_{O} = I_{MAX}, V_{I} = 3.3 \text{ V}$ |                    | 45  |                    | $\mu V_{RMS}$ |

| ton              | Turnon time           | See Note 2                                                                      |                    |     | 80                 | μs            |

| toff             | Turnoff time          | No load, See Note 3                                                             |                    | 1   | 5                  | ms            |

| I(Quiescent)     | Quiescent current     | I <sub>O</sub> = 1 mA                                                           |                    |     | 150                | μA            |

# regulator 1 voltage DET

|                 | PARAMETER                    | TEST CONDITIONS                                      | MIN  | TYP   | MAX  | UNIT |

|-----------------|------------------------------|------------------------------------------------------|------|-------|------|------|

|                 |                              | V <sub>REG1</sub> ≤ V <sub>TH</sub> −V <sub>HY</sub> |      | 0     | 0.3  |      |

| VO              | Voltage at XRST (see Note 4) | V <sub>REG1</sub> ≥ V <sub>TH</sub>                  |      | VREG1 |      | V    |

| V <sub>HY</sub> | Hysteresis Voltage           |                                                      | 80   | 100   | 120  | mV   |

|                 | Time delay voltage at CD1    |                                                      | 1.15 | 1.2   | 1.25 | V    |

|                 | Time delay current at CD1    |                                                      | 0.7  | 1     | 1.3  | μA   |

NOTE 4:  $V_{TH}$  is 90% of the nominal  $V_{REG1}$ .

# LED driver

|                  | PARAMETER             | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|------------------|-----------------------|--------------------------|-----|-----|-----|------|

|                  | Output current at IL0 | V <sub>IL0</sub> = 0.8 V |     |     | 160 | mA   |

|                  | Output current at IL1 | V <sub>IL1</sub> = 0.8 V |     |     | 20  | mA   |

|                  | Output current at IL2 | V <sub>IL2</sub> = 0.8 V |     |     | 10  | mA   |

| l <sub>lkg</sub> | Leakage current       | Off                      |     |     | 1   | μΑ   |

SLVS280 – MARCH 2001

# electrical characteristics (continued)

# vibrator driver

|              | PARAMETER         | TEST CONDITIONS                                                 | MIN  | TYP | MAX  | UNIT |

|--------------|-------------------|-----------------------------------------------------------------|------|-----|------|------|

| VO           | Output voltage    | SEL = H                                                         | 2.88 | 3   | 3.12 | V    |

| lo           | Output current    | SEL = H                                                         |      |     | 85   | mA   |

| VO           | Output voltage    | SEL = L                                                         | 1.17 | 1.3 | 1.43 | V    |

| IO           | Output current    | SEL = L                                                         |      |     | 140  | mA   |

| Vs           | Line regulation   | $V_{DD5}$ = 3.3 V to 4.3 V, I <sub>OUT</sub> = I <sub>MAX</sub> |      |     | 20   | mV   |

|              | Load regulation   | $I_{OUT} = 1 \text{ mA to } I_{MAX}, V_{DD5} = 3.8 \text{ V}$   |      |     | 80   | mV   |

| I(Quiescent) | Quiescent current | IOUT = 0                                                        |      |     | 80   | μΑ   |

| ۱L           | Current limit     | $V_O = 0$ , $V_{DD5} = 3.3$ V to 4.3 V                          |      |     | 490  | mA   |

# ring driver

| PARAMETER        |                 | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|------------------|-----------------|-----------------------------------|-----|-----|-----|------|

|                  | On resistance   | I <sub>out</sub> = 100 mA at 25°C |     |     | 3   | Ω    |

| l <sub>lkg</sub> | Leakage current | Off                               |     |     | 1   | μΑ   |

# battery charger control

| PAF              | RAMETER                | TEST CONDITIONS                                                                          | MIN                | TYP              | MAX   | UNIT |

|------------------|------------------------|------------------------------------------------------------------------------------------|--------------------|------------------|-------|------|

|                  | 0 <i>i</i> 1 <i>i</i>  | V(BREG) = 4.1 V                                                                          | 4.059              | 4.1              | 4.141 |      |

| VDD1             | System V <sub>DD</sub> | V <sub>(BREG)</sub> = 4.2 V (see function control register)                              | 4.158              | 4.2              | 4.242 | V    |

| V <sub>REF</sub> |                        | Required 0.1 $\mu\text{F}$ capacitor ESR of 2 $\Omega$ , load = 1 mA maximum             | 2.91               | 3                | 3.09  | V    |

| V(current sense) | Current sense voltage  | Set maximum current, 100 to 200, in 20-mV steps with I <sup>2</sup> C. See CSV register. | V <sub>sense</sub> |                  | mV    |      |

|                  | VGH                    | IGH = -0 mA                                                                              |                    | VCHG             |       | V    |

| VG               | VGL                    | IGL = -0 mA                                                                              |                    | 0                |       | V    |

| 10               | IGH                    |                                                                                          | 149                | 178.5            | 197   |      |

| IG               | IGL                    | VG = 2 V                                                                                 | 214                | 218              | 226   | μA   |

|                  | VG2H                   | IG2H = 0 mA                                                                              |                    | VBAT             |       |      |

| VG2              | VG2L                   | IG2L = 0 mA                                                                              |                    | 0                |       | V    |

| 100              | IG2H                   | VG2 = VBAT - 0.3 V                                                                       | -2.8               | -4.03            | -4.65 |      |

| IG2              | IG2L                   | VG2 = 0.3 V                                                                              | 3.2                | 5.02             | 5.70  | mA   |

|                  | VG3H                   | IG3H = -0 mA                                                                             |                    | V <sub>DD1</sub> |       |      |

| VG3              | VG3L                   | IG3L = 0 mA                                                                              |                    | 0                |       | V    |

| 102              | IG3H                   | VG3 = V <sub>DD1</sub> - 0.3 V                                                           | -2.7               | -3.87            | -4.65 |      |

| IG3              | IG3L                   | VG3 = 0.3 V                                                                              | 2.95               | 4.43             | 5.3   | mA   |

# electrical characteristics (continued)

# battery charger control (continued)

|                      | PARAMETER            | TEST CONDITIONS                          | MIN   | TYP  | MAX   | UNIT |

|----------------------|----------------------|------------------------------------------|-------|------|-------|------|

| VBAT regulation (CV) |                      | V <sub>(BREG)</sub> = 4.1 V (See Note 5) | 4.059 | 4.1  | 4.141 | N/   |

|                      |                      | $V_{BREG} = 4.2 V$                       | 4.158 | 4.2  | 4.242 | V    |

|                      | Low voltage cutoff   |                                          |       | 1.9  |       |      |

|                      | High voltage cutoff  |                                          |       | 4.45 |       |      |

| VBAT                 | Fast charge voltage  |                                          |       | 3.2  |       | V    |

|                      | Precharge voltage    | (see Note 6)                             | 1.9   | 2.05 | 2.2   |      |

|                      | Pack wake-up voltage |                                          | 4.214 | 4.30 | 4.386 |      |

| I <sub>cc</sub>      | Operating current    |                                          |       | 20   |       | mA   |

NOTES: 5. V<sub>(BREG)</sub> is the regulated battery voltage programmed by setting bit1 of CSV register.

6. Precharge current set by

$$I_{pre} = \frac{VRPC}{RPC} \times 45$$

where  $V_{RPC} = 1.2 V \pm 10\%$

# **ADC** specification

| TEST CONDITIONS                   | MIN                       | TYP                       | MAX                                                                                                                                       | UNIT                                                                                                                                             |

|-----------------------------------|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Output impedance < 100 k $\Omega$ |                           | 8                         |                                                                                                                                           | bit                                                                                                                                              |

| Confirm monotonous (see Note 7)   | -1                        |                           | 1                                                                                                                                         | LSB                                                                                                                                              |

| ADC output = 00H                  | 0                         |                           | 0.1                                                                                                                                       | V                                                                                                                                                |

| ADC output = FFH                  | 1.9                       | 2                         | 2.1                                                                                                                                       | V                                                                                                                                                |

|                                   |                           | 3                         |                                                                                                                                           | pF                                                                                                                                               |

|                                   | 450                       | 500                       | 550                                                                                                                                       | kHz                                                                                                                                              |

| From the start of SETUP           |                           | 16                        |                                                                                                                                           | CLK                                                                                                                                              |

| From the ADEN up selection        |                           |                           | 10                                                                                                                                        | μs                                                                                                                                               |

|                                   | Output impedance < 100 kΩ | Output impedance < 100 kΩ | Output impedance < 100 k $\Omega$ 8Confirm monotonous (see Note 7)-1ADC output = 00H0ADC output = FFH1.923450500From the start of SETUP16 | Output impedance < 100 kΩ8Confirm monotonous (see Note 7) $-1$ 1ADC output = 00H00.1ADC output = FFH1.922.1333450500550From the start of SETUP16 |

NOTE 7: LSB =  $\frac{2V}{255}$  = 7.8 mV

# logic level output

| PARAMETER                     | TEST CONDITION                                                            | MIN      | MAX               | UNIT |

|-------------------------------|---------------------------------------------------------------------------|----------|-------------------|------|

| VOH of terminals PWRKOUT, IRQ | $I_{OH} = -2 \text{ mA}$                                                  | 0.8VREG1 | V <sub>REG1</sub> | V    |

| VOL of terminals PWRKOUT, IRQ | $I_{OL} = 2 \text{ mA}$                                                   | GND      | 0.22VREG1         | V    |

| V <sub>OL</sub> of DATA       | $I_{OL} = 2 \text{ mA}$                                                   | GND      | 0.22VREG1         | V    |

| V <sub>OH</sub> of XRST       | $I_{OH} = -2 \text{ mA}$ (open drain with 100-k $\Omega$ internal pullup) |          | V <sub>REG1</sub> | V    |

| V <sub>OL</sub> of XRST       | $I_{OL} = 2 \text{ mA}$ (open drain 100-k $\Omega$ internal pullup)       | GND      | 0.22VREG1         | V    |

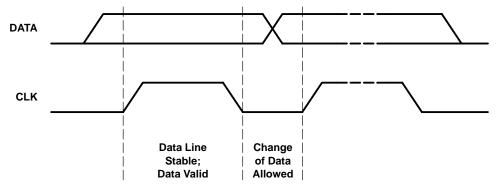

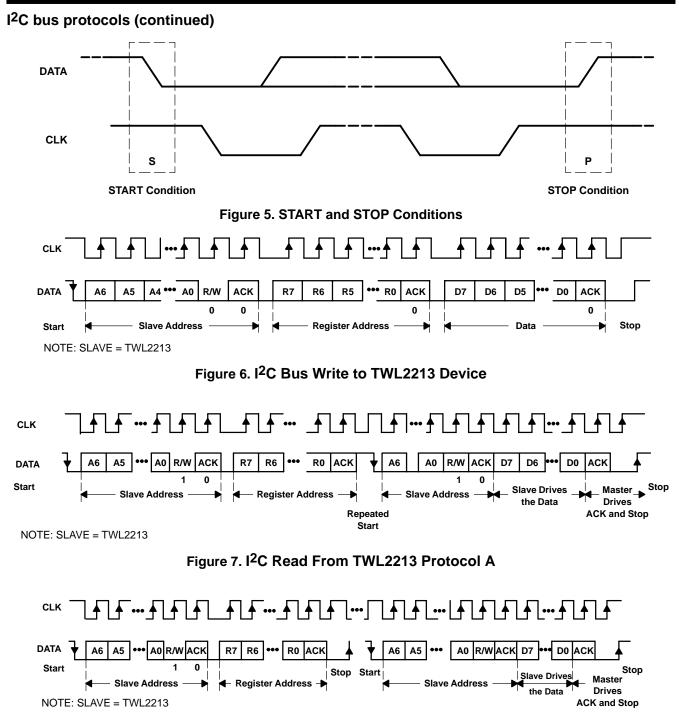

# I<sup>2</sup>C bus protocols

The TWL2213 serial interface is designed to be I<sup>2</sup>C bus compatible, operating in the slave mode. This interface consists of the following terminals:

CLK: I<sup>2</sup>C bus serial clock. This input synchronizes the control data transfer from and to the microprocessor.

DATA: I<sup>2</sup>C bus serial address/data input/output. This is a bidirectional terminal that transfers registers, control addresses, and data into and out of the microprocessor. This terminal is an open drain and requires a pullup resistor of 10 k $\Omega$  to V<sub>REG1</sub>.

The TWL2213 device has a fixed device select addresses of E4h for write mode and E5h for read mode. For normal data transfer, DATA is allowed to change only when CLK is low. Changes when CLK is high are reserved for indicating the start and stop conditions. Data transfer may be initiated only when the bus is not busy (both DATA and CLK lines remain high). During data transfer, the data line must remain stable whenever the clock line is at high. There is one clock pulse per bit of data. Each data transfer is initiated with a start condition and terminated with a stop condition. When addressed, the TWL2213 device generates an acknowledge after the reception of each byte. The master device (microprocessor) must generate an extra clock pulse that is associated with the acknowledge bit. The TWL2213 device must pull down the DATA line during the acknowledge clock pulse so that the DATA line is at stable low state during the high period of the acknowledge clock pulse. Setup and hold times must be taken into account. During read operations, a master must signal the end of data to the slave by not generating an acknowledge bit on the last byte that was clocked out of the slave. In this case, the slave TWL2213 device must leave the data line high to enable the master to generate the stop condition.

Figure 4. Bit Transfer on the I<sup>2</sup>C Bus

Figure 8. I<sup>2</sup>C Read From TWL2213 Protocol B

SLVS280 - MARCH 2001

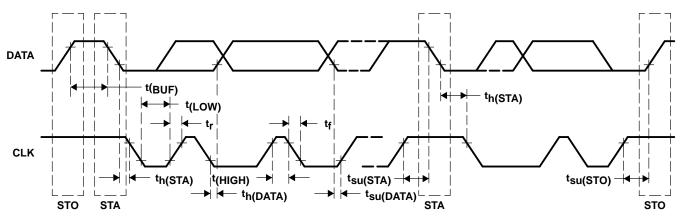

# I<sup>2</sup>C timing

|                                                                                                           | MIN  | MAX | UNIT |

|-----------------------------------------------------------------------------------------------------------|------|-----|------|

| Clock frequency, f <sub>max</sub>                                                                         |      | 400 | kHz  |

| Clock high time, t <sub>wH</sub> (HIGH)                                                                   | 600  |     | ns   |

| Clock low time, t <sub>wL(LOW)</sub>                                                                      | 1300 |     | ns   |

| DATA and CLK rise time, t <sub>r</sub>                                                                    |      | 300 | ns   |

| DATA and CLK fall time, t <sub>f</sub>                                                                    |      | 300 | ns   |

| Hold time (repeated) START condition (after this period the first clock pulse is generated), $t_{h(STA)}$ | 600  |     | ns   |

| Setup time for repeated START condition, th(DATA)                                                         | 600  |     | ns   |

| Data input hold time, th(DATA)                                                                            | 0    |     | ns   |

| Data input setup time, t <sub>SU(DATA)</sub>                                                              | 100  |     | ns   |

| STOP condition setup time, t <sub>su(STO)</sub>                                                           | 600  |     | ns   |

| Bus free time, t <sub>(BUF)</sub>                                                                         | 1300 |     | ns   |

| Figure 9 | ). I <sup>2</sup> C-Bus | Timing | Diagram |

|----------|-------------------------|--------|---------|

|----------|-------------------------|--------|---------|

# register map

| REGISTER                                                                 | ADDRESS<br>(HEX) | D7<br>(MSB)                                             | D6                                      | D5                | D4                                                    | D3                                | D2 | D1 | D0<br>(LSB) |  |

|--------------------------------------------------------------------------|------------------|---------------------------------------------------------|-----------------------------------------|-------------------|-------------------------------------------------------|-----------------------------------|----|----|-------------|--|

| PTR: Precharge timer register                                            | 10h<br>(R/W)     | 0 = Disable<br>1 = Enable                               |                                         |                   |                                                       |                                   |    |    |             |  |

|                                                                          | Default          | 0                                                       | 0                                       | 0                 | 0                                                     | 0                                 | 0  | 1  |             |  |

| CCTR: CC charge timer register                                           | 11h<br>(R/W)     | 0 = Disable<br>1 = Enable                               | 00000 = 0 minut<br>:<br>11111 = 273 min | nutes in 8-minute | steps                                                 | Don't care                        |    |    |             |  |

| •                                                                        | Default          | 0                                                       | 0                                       | 0                 | 0                                                     | 0                                 | 0  |    |             |  |

| TCTR: Total charge timer<br>(CC+CV) register                             | 12h<br>(R/W)     | 0000 = 0 hours<br>:<br>1111 = 15 hours                  | s in 1-hour steps                       |                   |                                                       | Don't care                        |    |    |             |  |

|                                                                          | Default          | 1                                                       | 1                                       | 1                 | 1                                                     |                                   |    |    |             |  |

| VBOTRH+: Battery over<br>temperature register at<br>High+                | 13h<br>(R/W)     | 00h = 0 V<br>:<br>FFh = 2 V                             |                                         |                   |                                                       |                                   |    |    |             |  |

| Hign+                                                                    | Default          | 00h = 0 V                                               |                                         |                   |                                                       |                                   |    |    |             |  |

| VBOTRH-: Battery over<br>temperature register at                         | 14h<br>(R/W)     | 00h = 0 V<br>:<br>FFh = 2 V                             |                                         |                   |                                                       |                                   |    |    |             |  |

| High–                                                                    | Default          | 00h = 0 V                                               |                                         |                   |                                                       |                                   |    |    |             |  |

| VBOTRL: Battery over temperature register at low                         | 15h<br>(R/W)     | 00h = 0 V<br>:<br>FFh = 2 V                             |                                         |                   |                                                       |                                   |    |    |             |  |

|                                                                          | Default          | 00h = 0 V                                               |                                         |                   |                                                       |                                   |    |    |             |  |

| <b>CSV:</b> Charge current sensing voltage and termination current ratio | 16h<br>(R/W)     | Sensing voltage<br>000 = 100 mV<br>:<br>101 = 200 mV in |                                         |                   | Termination curr<br>000 = 10%<br>:<br>100 = 50% in 10 | 0 = 4.1 V<br>1 = 4.2 V Don't care |    |    |             |  |

|                                                                          | Default          | 0                                                       | 0                                       | 0                 | 0                                                     | 0                                 | 0  | 0  | 1           |  |

| ADBV: Battery voltage                                                    | 17h<br>(R)       | $VABV = 2 V \times 2$                                   | 2.5 × Value/256                         |                   |                                                       |                                   |    |    |             |  |

| ADBT: Battery temperature voltage                                        | (R)              | VADBAT = 2 V :                                          | $\times$ Value/256                      |                   |                                                       |                                   |    |    |             |  |

| ADCIN1: Voltage                                                          | 19h<br>(R)       | VADCIN1 = 2 V                                           | / × Value/256                           |                   |                                                       |                                   |    |    |             |  |

| ADCIN2: Voltage                                                          | 1Ah<br>(R)       | VADCIN2 = 2 V                                           | $/ \times$ Value/256                    |                   |                                                       |                                   |    |    |             |  |

### charger (continued)

| REGISTER               | ADDRESS<br>(HEX) | D7<br>(MSB)                                         | D6                                                              | D5                                                                     | D4                                                              | D3                                                                          | D2                                                           | D1                                                           | D0<br>(LSB)                                     |

|------------------------|------------------|-----------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------|

| FCR1: Function control | 1Bh<br>(R/W)     | CHGSTR<br>0 =<br>1 = Charger<br>start<br>See Note 8 | ADC status<br>0 = Disable<br>1 = Enable<br>See Notes 8<br>and 9 | ADC function<br>0 = Single<br>1 = Periodically<br>See Notes 8<br>and 9 | ADBV<br>0 = Disable<br>1 = Enable<br>See Notes 8<br>and 10      | VTS<br>0 = Disable<br>1 = Enable<br>See Notes 8<br>and 11                   | ADCIN1<br>0 = Disable<br>1 = Enable<br>See Notes 8<br>and 11 | ADCIN2<br>0 = Disable<br>1 = Enable<br>See Notes 8<br>and 11 | IRQ<br>0 = IRQ is L<br>1 = IRQ is H             |

|                        | Default          | 0                                                   | 0                                                               | 0                                                                      | 0                                                               | 0                                                                           | 0                                                            | 0                                                            | 0                                               |

| SR: STATUS register    | 1Ch<br>(R)       | VEXT<br>1 = VCCHG in<br>range                       | BATERR<br>1 = Battery<br>error                                  | VBOT<br>1 = Battery<br>overvoltage                                     | CTERM<br>1 = Charge<br>current goes<br>below<br>termination out | NOCHG<br>1 = A charge<br>condition,<br>reset<br>CHGSTR to 0.<br>See Note 12 | PCHG<br>1 = Precharge<br>mode                                | CCTO<br>1 = CC charge<br>timeout                             | TCTO<br>1 = Total<br>charge time<br>(CC+CV) out |

NOTES: 8. After TWL2213 has finished charging, these values are set to 0.

- 9. During CHGSTR H, ADC enables and periodically keeps functioning.

- 10. During charging mode, ADVB is enabled automatically.

- 11. Charging mode is not necessary to set enable for function.

- 12. External microprocessor must set CHGSTR bit to 0 when NOCHG = 1

# regulator, LED, VIBRATOR

| REGISTER                  | ADDRESS<br>(HEX)                        | D7<br>(MSB)                              | D6                                 | D5                        | D4                        | D3                        | D2                                            | D1          | D0<br>(LSB) |  |

|---------------------------|-----------------------------------------|------------------------------------------|------------------------------------|---------------------------|---------------------------|---------------------------|-----------------------------------------------|-------------|-------------|--|

|                           |                                         |                                          | RE                                 | G2                        |                           |                           | RE                                            | G3          |             |  |

| FCR2: Function register 2 | 20h<br>(R/W)                            | 0 = Disable<br>1 = Enable                | 000 = 3 V<br>:<br>111 = 2.3 V in 1 | 00-mV steps               |                           | 0 = Disable<br>1 = Enable | 000 = 3 V<br>:<br>111 = 2.3 V in 10           | 00-mV steps |             |  |

|                           | Default                                 | 0                                        | 0                                  | 0                         | 0                         | 0                         | 0                                             | 0           | 0           |  |

|                           |                                         |                                          | RE                                 | G4                        |                           |                           | RE                                            | G5          |             |  |

| FCR3: Function register 3 | 21h<br>(R/W)                            | 0 = Disable<br>1 = Enable                | 000 = 3 V<br>:<br>101 = 2.5 V in 1 | 00-mV steps               |                           | 0 = Disable<br>1 = Enable | 000 = 3 V<br>:<br>101 = 2.5 V in 100-mV steps |             |             |  |

|                           | Default                                 | 0                                        | 0                                  | 0                         | 0                         | 0                         | 0                                             | 0           | 0           |  |

|                           |                                         |                                          | RE                                 | G6                        | -                         |                           |                                               |             |             |  |

| FCR4: Function register 4 | 22h<br>(R/W)                            | 0 = Disable<br>1 = Enable<br>See Note 13 | 000 = 3 V<br>:<br>101 = 2.5 V in 1 | 00-mV steps               |                           |                           | Don't care                                    |             |             |  |

|                           | Default                                 | 0                                        | 0                                  | 0                         | 0                         |                           |                                               |             |             |  |

|                           | 23                                      | Vibrator                                 | Ringer                             | IL2                       | IL1                       | IL0                       |                                               |             |             |  |

| FCR5: Function register 5 | Exaction register 5 $(R/W)$ 0 = Disable | 0 = Disable<br>1 = Enable                | 0 = Disable<br>1 = Enable          | 0 = Disable<br>1 = Enable | 0 = Disable<br>1 = Enable | 0 = Disable<br>1 = Enable |                                               | Don't care  |             |  |

|                           | Default                                 | 0                                        | 0                                  | 0                         | 0                         | 0                         | 1                                             |             |             |  |

NOTE 13: CONT = H REG6 is dependent on D7 to enable, CONT = L REG6 is independent of D7, always on after power up

SLVS280 - MARCH 2001

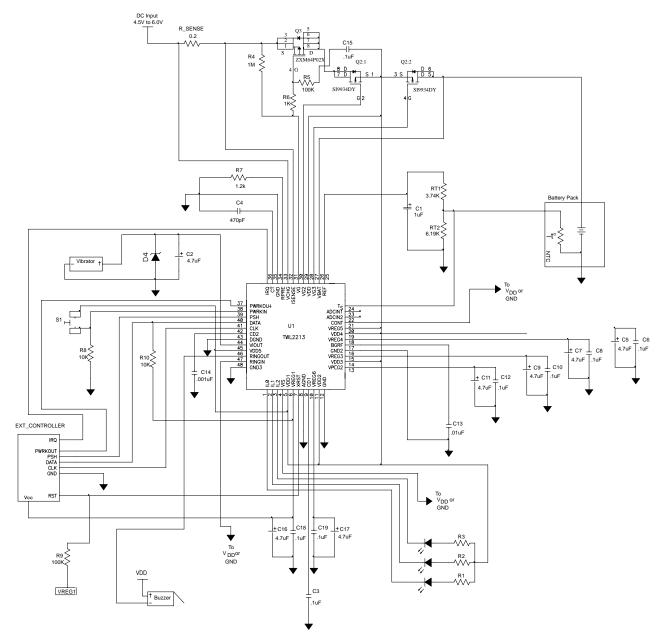

# **APPLICATION INFORMATION**

**Figure 10. Typical Application Circuit**

SLVS280 - MARCH 2001

# **APPLICATION INFORMATION**

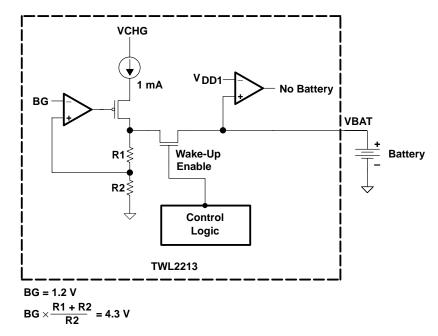

# device power supply control (V<sub>DD1</sub>)

The TWL2213 device receives device power by regulating the VCHG input to 4.1 V or 4.2 V, whenever VCHG is available; otherwise, the device uses the VBAT input directly as device dc supply. The regulated voltage from VCHG is programmable through the  $I^2C$  interface.

Figure 11. Device Power Supply

Condition 1: VCHG is on (VG = Active, VG2 = On, VG3 = Off)

$$V_{DD1} = BG \times \frac{R1 + R2}{R2} = 4.1 \text{ V or } 4.2 \text{ V}$$

TWL2213 device sets R2 value according to the programmed voltage level (4.1 V or 4.2 V).

Condition 2: VCHG is Off and VBAT applied (VG = High, VG2 = Off, VG3 = On)

$$V_{DD1} = VBAT$$

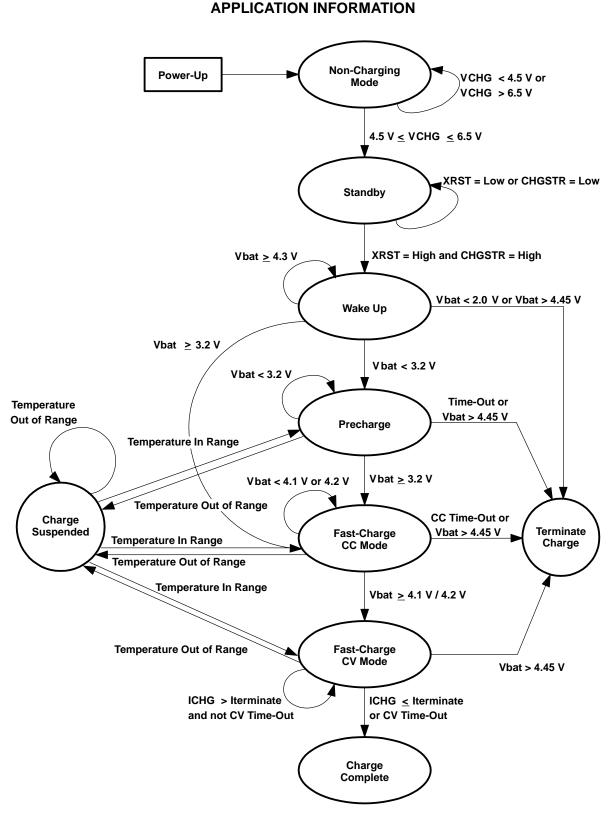

# battery charger

The TWL2213 device provides a charger function for single cell Li-Ion battery packs. The charging activity starts with the battery pack wake-up cycle. If the wake-up cycle completes successfully, the charger starts the precharge function and slowly charges the battery to 3.2 V. If the battery is charged to 3.2 V within the time limit, the charger goes into the fast charge mode. The fast charge mode has two phases: 1) constant current mode (CC) and 2) constant voltage mode (CV). The charger starts CC mode with the maximal charging current until the battery voltage reaches the regulated voltage level. The charger is then switched to CV mode. During the CV mode, the TWL2213 device monitors the charging current; once it is below the programmed termination current level, the charger activity is terminated. The termination current level can be programmed at 10%, 20%, 30%, 40%, or 50% of the maximum charging current at the CC mode.

SLVS280 - MARCH 2001

Figure 12. Charger State Diagram

SLVS280 - MARCH 2001

# **APPLICATION INFORMATION**

# control register—FCR1 (1BH)

| BIT | NAME            | DESCRIPTION                                                                                                                                                          |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CHGSTR          | Set this bit to 1 to start the charger operation. This bit is cleared if the charger is terminated. (Refer to status register table below for terminated conditions) |

| 6   | ADC<br>ENABLE   | Set this bit to 1 to enable ADC operation, 0 to stop.                                                                                                                |

| 5   | ADC<br>Function | Set this bit to 1 to have ADC operate continuously. Set to 0 to have ADC to operate one cycle only.                                                                  |

| 4   | ADBV            | Set this bit to 1 to enable the VBAT input channel to ADC. 0: disable.                                                                                               |

| 3   | VTS             | Set this bit to 1 to enable the VTS input channel to ADC. 0: disable.                                                                                                |

| 2   | ADCIN1          | Set this bit to 1 to enable the ADCIN1 input channel.                                                                                                                |

| 1   | ADCIN2          | Set this bit to 1 to enable the ADCIN2 input channel.                                                                                                                |

| 0   | IRQ             | Status of IRQ pin (refer to IRQ operation section).                                                                                                                  |

ADC has four input channels (ADBV, VTS, ADCIN1, ADCIN2). Each channel can be enabled or disabled individually. The selected channel must be enabled before ADC FUNCTION and ADC ENABLE bits are enabled, the channel is included in the ADC operation.

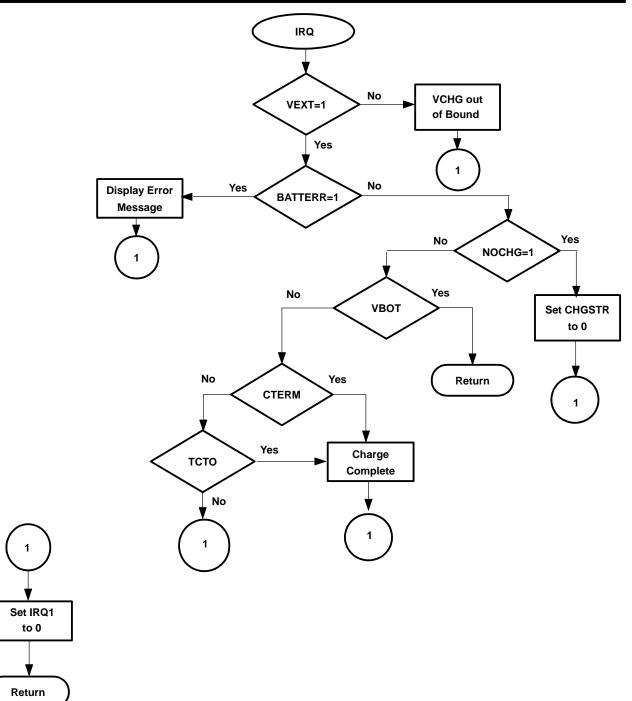

### IRQ control/status

TWL2213 uses the IRQ signal to inform the external controller about the exception condition of the VCHG input and the charger status. Bit0 reflects the state of the IRQ signal. IRQ occurs in the following five conditions:

- 1. VCHG returns to operating range from non\_operating range.

- 2. VCHG goes out of range from operating range.

- 3. Battery error—occurs only during the charging cycle.

- 4. Battery temperature out of range—occurs only during the charging cycle. The charger is suspended temporarily. IRQ is cleared when the temperature returns to normal and the charger resumes automatically.

- 5. Charge complete.

The controller must clear the IRQ signal by writing 0 to Bit0 in the interrupt service routine, except in the VBOT condition. The controller may miss the next interrupt if it fails to write the 0. In VBOT condition, TWL2213 clears the IRQ when the condition goes away.

### status register description—SR (1CH)

SR shows the status of the charger. The external controller reads the SR to track the state of the charging condition.

| BIT | NAME   | DESCRIPTION     When Vext = 1 the VCHG input is in the operating range. Otherwise the VCHG is out of range.                                                                                                                                                                                                                                                                                            |  |  |  |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | VEXT   |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 6   | BATERR | This bit is set to 1 indicating battery error. Four cases cause battery error: pre-charge timeout, constant-current mode timeout, VBAT < 2.9 V, or VBAT > 4.45 V.                                                                                                                                                                                                                                      |  |  |  |

| 5   | VBOT   | During the charging cycle, if the battery temperature exceeds or falls below the nominal range, this sets to 1. The charger is suspended temporarily. VBOT is cleared when the temperature returns to nominal range and the charger function resumes automatically.                                                                                                                                    |  |  |  |

| 4   | CTERM  | The charger is terminated normally because the charging current is below the preset termination current value.                                                                                                                                                                                                                                                                                         |  |  |  |

| 3   | NOCHG  | No charge condition. This condition is detected only during the wake_up state of the charging function. After the 8-second wake up period expires, if VBAT is above 4.3 V, the NOCHG flag is set. The cause of this is a missing or completely charged battery. The TWL2213 does not deactivate the charger by setting CHGSTR = 0. The external processor must turn off the CHGSTR by setting it to 0. |  |  |  |

| 2   | PCHG   | Set to 1 to indicate the charger is in pre-charge state.                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 1   | ССТО   | Set to 1 to indicate the charging time has exceeded the time limit allowed during CC-mode. This is a fatal error. TWL2213 clears CHGSTR bit, sets the BATERR flag, and makes IRQ go high to interrupt the external controller.                                                                                                                                                                         |  |  |  |

| 0   | тсто   | Set to 1 to indicate the charging time has exceeded the overall time limit allowed during CV-mode. This is treated as normal termination of the charger function. TWL2213 clears the CHGSTR bit and sets IRQ to 1 to interrupt the external controller.                                                                                                                                                |  |  |  |

SLVS280 - MARCH 2001

### battery pack wake up

Li-lon cells can be easily damaged by overcharging or overdischarging. To prevent damage, a pack-protector device is used within the battery pack. During the charging cycle, if the pack-protector senses an over-voltage condition, it disconnects the pack from the charger to prevent further charging but allows discharging. During the discharging cycle, if the protector senses an under-voltage condition, it disconnects the cell from the load to prevent further discharging.

This phase of the charging cycle provides wake-up capability for the battery pack with a pack-protector device. At the start of the charge cycle, the TWL2213 device provides a wake-up signal of 1 mA and 4.3 V to the battery pack. At the end of the 8-second time limit, if the battery pack voltage remains at 4.3 V, a no-battery flag is set in the status register to signal the condition that the charging path is open. If the battery voltage is below 2.5 V, a BATTERR flag is set in the status register to signal a bad battery cell. In either case, the charging activity is halted.

### Figure 14. Battery Pack Wake Up

# precharge

The TWL2213 device starts the precharge phase when the battery voltage is less than 3.2 V. The precharge time is limited by the PTR timer. The precharge current level is set by an external resistor. The maximum precharge current the charger can supply is 100 mA. Use the following equation to choose the external resistor value.

$$Rpr = \frac{V_{PRE}}{Ipre} \times 45, V_{PRE} = 1.2V \pm 10\%$$

Where:

Rpr = External resistor (ohm) Ipre = Desired precharge current (Amp) V<sub>PRE</sub> = Voltage at RPRE Pin (Volts)

SLVS280 - MARCH 2001

# **APPLICATION INFORMATION**

Figure 15. Precharge Functional Diagram

# fast charge constant current (CC mode)

When the battery voltage is 3.2 V or higher, the TWL2213 device starts the fast charge CC mode cycle. In CC mode, the charger regulates the charging current to its maximum level. The maximum charging current (Imax) is determined by the external sense resistor, Rsense, and the voltage, Vsense. Vsense is programmable through the I<sup>2</sup>C interface (refer to CSV register for programming information). The range of Vsense is from 100 mV to 200 mV, in 20-mV steps. The CC mode charge time is limited by the CCTR timer.

$\mathsf{Imax} = \frac{\mathsf{Vsense}}{\mathsf{Rsense}}$

# fast charge constant current (CV mode)

When the cell reaches the constant voltage phase, the charger switches to the fast charge CV mode. The charging current begins tapering down while the charging voltage is regulated at the programmed voltage level (4.1 V or 4.2 V). The CV mode charging is limited by the TCTR timer.

Figure 16. Fast Charge Functional Diagram

# APPLICATION INFORMATION

### current termination

During the CV mode, the charge cycle is terminated when the charging current is under the programmed terminated level or when the total charge timer (TCTR) times out. The terminated current level can be programmed to 10%, 20%, 30%, 40%, or 50% of the charging current at CC mode.

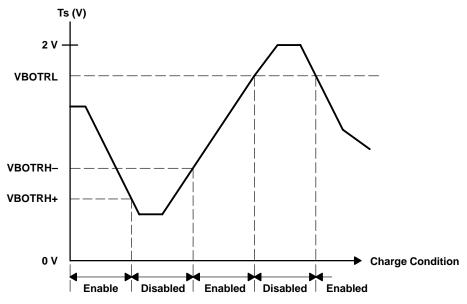

# temperature monitoring

The TWL2213 device monitors the battery temperature throughout the charge cycle. The input for ADC reference voltage is generated by a negative temperature coefficient (NTC) thermistor. The TWL2213 device compares the ADC input reference voltage to the programmed threshold voltages to determine if charging is allowed. Three required thresholds are:

- VBOTRH+ Voltage for over-temperature cutoff; charging is suspended.

- VBORTH– Voltage to resume charging function for over-temperature cutoff.

- VBORTL Voltage for low-temperature cutoff; charging is suspended.

### Figure 17. Temperature Monitoring

NOTE: The power-up default values are zero for these three thresholds. If the user opts not to use the temperature monitoring function during the charge cycle, the TS pin of the IC must be tied to the GND to avoid an arror signal.

# maximum time out

The TWL2213 device provides three timers for maximal time allowed for charging. The time is programmable through  $I^2C$  interface.

| TIMER                    | RANGE     | STEP  | COMMENT                                                                                                                                                                      |

|--------------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Precharge timer (PTR)    | 0–136 min | 4 min | During the precharge cycle, if the timer expires before the precharging activity is complete, a BATT_ERR flag is set in the status register, and the charge is terminated.   |

| CC charge timer (CCTR)   | 0–274 min | 8 min | During the CC mode cycle, if the timer expires before the CC activity is complete, a BATT_ERR flag is set in the status register, and the charge is terminated.              |

| Total charge timer (TCTR | 0–15 hr   | 1 hr  | Total charge time is defined as the total charge time of CC mode and CV mode. TCTR time-out occurs only in the CV mode. If the timer expires before, the charge is complete. |

SLVS280 - MARCH 2001

MECHANICAL DATA

### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

### **IMPORTANT NOTICE**